WikiDer > HyperSPARC

| Общая информация | |

|---|---|

| Запущен | 1993 |

| Снято с производства | 1996 |

| Разработано | Росс Технологии |

| Спектакль | |

| Максимум. ЦПУ тактовая частота | От 40 МГц до 200 МГц |

| Архитектура и классификация | |

| Набор инструкций | SPARC V8 |

| Физические характеристики | |

| Ядра |

|

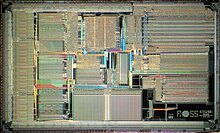

В hyperSPARCпод кодовым названием "Pinnacle" - это микропроцессор который реализует SPARC версии 8 архитектура набора команд (ISA) разработано Росс Технологии за Cypress Semiconductor.

HyperSPARC был представлен в 1993 году и конкурировал с Sun Microsystems SuperSPARC. Раджу Вегесна был микроархитектором. HyperSPARC был основным конкурентом Sun Microsystem в середине 1990-х годов. Когда Fujitsu приобрела Ross у Cypress, новый владелец считал HyperSPARC более важным, чем SPARC64 разработан Компьютерные системы HAL, также дочерняя компания Fujitsu, мнение, которое разделили с аналитиками.

Описание

HyperSPARC был двусторонним суперскалярный микропроцессор. У него было четыре исполнительных блока: целочисленный блок, блок с плавающей запятой, блок загрузки / сохранения и блок ветвления. HyperSPARC имеет встроенный кэш команд объемом 8 КБ, из которого за цикл выбирались и декодировались две инструкции. Декодер не мог декодировать новые инструкции, если ранее декодированные инструкции не были переданы исполнительным блокам.

Целое число зарегистрировать файл содержал 136 регистров, обеспечивая восемь зарегистрировать окна, функция, определенная в SPARC ISA. У него было два порта чтения. Целочисленный блок имел четырехступенчатый трубопровод, из которых были добавлены две стадии, чтобы конвейер был равен всем конвейерам с плавающей запятой. Инструкции целочисленного умножения и деления, добавленные в версию V8 архитектуры SPARC, имели задержку 18 и 37 циклов соответственно и останавливали конвейер, пока они не были выполнены.

Поддерживаемый микропроцессор многопроцессорность на MBus системы.

Физический

HyperSPARC состоит из 1,2 миллиона транзисторов. Он был изготовлен Cypress из двухслойного металла толщиной 0,65 мкм, комплементарный металл – оксид – полупроводник (CMOS) процесс. Более поздние версии hyperSPARC имеют больше транзисторов из-за новых функций и были перенесены на более новые процессы. Они были изготовлены Fujitsu, за исключением последней итерации, которую изготовил NEC.

Упаковка

HyperSPARC был многочиповой конструкцией. Он был упакован в керамический многокристальный модуль (MCM) с матрица сетки выводов (PGA).

Чипсеты

В hyperSPARC использовался набор микросхем Cypress SparcSet, представленный в конце июля 1992 года. Он был разработан стартапом Nimbus Technologies, Inc. в Санта-Кларе, Калифорния, для Cypress, который и разработал дизайн. SparcSet также был совместим с другими микропроцессорами SPARC.

Рекомендации

- Левин, Бернар (11 апреля 1994). «MCM выступает за соблазн потенциальных пользователей». Электронные новости.

- Холден, Дэниел (15 февраля 1993). «Кипарис, Солнце: гипертония HyperSPARC». Электронные новости.

- Холден, Дэниел (15 марта 1993 г.). «HyperSparc планирует объединиться с Intel в вопросе разработки процессора P6». Электронные новости.

- Холден, Дэниел (19 апреля 1993 г.). «HyperSPARC медленно работает с Sun Micro». Электронные новости.

- Шен, Джон Пол и Липасти, Микко Х. (2004). Современный дизайн процессора. McGraw-Hill Professional.

дальнейшее чтение

- «Росс представляет проект Pinnacle SPARC». (25 марта 1992 г.). Отчет микропроцессора, т. 6, вып. 4.

- «Битва TI и Сайпресс / Росс за лидерство в SPARC». (27 мая 1992 г.). Отчет микропроцессора, т. 6, вып. 7.

- "Росс наконец-то отправляет HyperSPARC". (15 ноября 1993 г.). Отчет микропроцессора, т. 7, вып. 15.

- «Усовершенствованный HyperSparc бросает вызов UltraSparc». (4 декабря 1995 г.). Отчет микропроцессора, т. 9, вып. 16.