WikiDer > Intel 8253

В Intel 8253 и 8254 находятся Программируемые интервальные таймеры (PIT), которые выполняют функции хронирования и подсчета с использованием трех 16-битных счетчиков.[1]

Семейство 825x было разработано в первую очередь для Intel 8080/8085-процессоры, но позже использовались в x86-совместимых системах. Чипы 825x или эквивалентная схема, встроенная в более крупный чип, встречаются во всех Совместимость с IBM PC, а советские компьютеры вроде Вектор 06C.

В устройствах, совместимых с ПК, канал таймера 0 назначен IRQ-0 (аппаратное прерывание с наивысшим приоритетом). Канал таймера 1 назначен на обновление DRAM (по крайней мере, в ранних моделях до 80386). Канал таймера 2 назначен на Динамик ПК.

Intel 82c54 (c для CMOS логика) обрабатывает тактовые сигналы с частотой до 10 МГц.[1]

История

8253 описан в публикации Intel "Каталог данных компонентов" 1980 года. 8254, описанный как расширенный набор 8253 с более высокими тактовыми частотами, имеет "предварительные" данные в "Каталоге данных компонентов" Intel 1982 года.

8254 реализован в HMOS и имеет команду «Обратное считывание», недоступную на 8253, и позволяет чередовать чтение и запись одного и того же счетчика.[2]

Совместимость с современными ПК, либо при использовании SoC Процессоры или южный мост обычно реализует полную совместимость с 8254 для обратной совместимости и взаимодействия.[3] Команда Read Back является важной функцией ввода-вывода для взаимодействия с многоядерными процессорами и графическими процессорами.

Варианты

Существует военная версия Intel M8253 с температурным диапазоном от -55 ° C до + 125 ° C, которая также имеет допуск по мощности 5V ± 10%.[4]

особенности

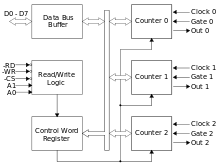

Таймер имеет три счетчика, пронумерованных от 0 до 2.[5] Каждый канал может быть запрограммирован на работу в одном из шести режимов. После программирования каналы работают независимо.[1]

Каждый счетчик имеет два входных контакта - «CLK» (Часы input) и «GATE» - и один вывод «OUT» для вывода данных. Три счетчика являются 16-битными счетчиками с обратным отсчетом, независимыми друг от друга, и могут быть легко прочитаны ЦПУ.[6]

- Буфер шины данных содержит логику для буферизации шины данных между микропроцессором и внутренними регистрами. Он имеет 8 входных контактов, обычно обозначенных как D7..D0, где D7 - это MSB.

- Логика чтения / записи имеет 5 контактов, которые перечислены ниже. "Икс"означает, что X - активный низкий сигнал.

- RD: читать сигнал

- WR: написать сигнал

- CS: сигнал выбора микросхемы

- A0, A1: адресные строки

Режим работы PIT изменяется установкой вышеуказанных аппаратных сигналов. Например, для записи в регистр управляющего слова необходимо установить CS=0, RD=1, WR= 0, А1 = А0 = 1.

- Регистр контрольного слова содержит запрограммированную информацию, которая будет отправлена ( микропроцессор) к устройству. Он определяет, как логически работает каждый канал PIT. Каждый доступ к этим портам занимает около 1 мкс.

Чтобы инициализировать счетчики, микропроцессор должен записать в этот регистр управляющее слово (CW). Это можно сделать, установив правильные значения для контактов блока логики чтения / записи, а затем отправив управляющее слово в блок буфера данных / шины.

Регистр управляющего слова содержит 8 битов, обозначенных D7..D0 (D7 - это MSB). Расшифровка несколько сложная. Большинство значений задают параметры для одного из трех счетчиков:

- Два старших бита (если не 11) выбирают регистр счетчика, к которому применяется команда.

- Следующие два бита (если не 00) выбирают формат, который будет использоваться для последующего доступа чтения / записи к регистру счетчика. Обычно это режим, в котором доступ чередуется между наименее значимыми и наиболее значимыми байтами. Одно различие между 8253 и 8254 заключается в том, что у первого был один внутренний бит, который влиял как на чтение, так и на запись, поэтому, если формат был установлен на 2-байтовый, чтение lsbyte привело бы к тому, что следующая запись будет направлена в msbyte. 8254 использовал отдельные биты для чтения и записи.

- Следующие три бита выбирают режим, в котором будет работать счетчик.

- Самый младший бит определяет, будет ли счетчик работать в двоичном или BCD. (Подсчет BCD почти никогда не используется и может быть неправильно реализован в эмуляторах или южных мостах.)

Однако есть две другие формы:

- Заблокируйте счетчик для данного таймера. При следующем чтении вместо значения счетчика в момент чтения будет возвращено значение счетчика в момент команды защелки. После завершения чтения последующие чтения вернут текущий счетчик. Когда используется команда защелки, режим и статус BCD не меняются.

- (Только 8254) Зафиксируйте состояние и / или счет для нескольких таймеров. Это позволяет использовать несколько одновременных команд защелки с использованием растрового изображения. Кроме того, текущая конфигурация канала может быть считана в дополнение к счетчику.

| Бит № / Имя | Краткое описание | |||||||

|---|---|---|---|---|---|---|---|---|

| D7 SC1 | D6 SC2 | D5 RW1 | D4 RW0 | D3 M2 | D2 M1 | D1 M0 | D0 BCD | |

| 0 | 0 | формат | Режим | BCD | Установить режим счетчика 0 | |||

| 0 | 1 | формат | Режим | BCD | Установить режим счетчика 1 | |||

| 1 | 0 | формат | Режим | BCD | Установить режим счетчика 2 (порт 42h) | |||

| 1 | 1 | считать | статус | C2 | C1 | C0 | Икс | Команда обратного чтения (только 8254) |

| счетчик | 0 | 0 | - Икс - | Значение счетчика защелки. При следующем чтении счетчика будет прочитан снимок значения. | ||||

| счетчик | 0 | 1 | Режим | BCD | Чтение / запись только младшего байта значения счетчика | |||

| счетчик | 1 | 0 | Режим | BCD | Чтение / запись только старшего байта значения счетчика | |||

| счетчик | 1 | 1 | Режим | BCD | 2 × Чтение / 2 × Запись младшего байта, затем старшего байта значения счетчика | |||

| счетчик | формат | 0 | 0 | 0 | BCD | Режим 0: прерывание по счетчику терминала | ||

| счетчик | формат | 0 | 0 | 1 | BCD | Режим 1: однократный запуск с аппаратным запуском | ||

| счетчик | формат | Икс | 1 | 0 | BCD | Режим 2: генератор скорости | ||

| счетчик | формат | Икс | 1 | 1 | BCD | Режим 3: прямоугольная волна | ||

| счетчик | формат | 1 | 0 | 0 | BCD | Режим 4: программный строб | ||

| счетчик | формат | 1 | 0 | 1 | BCD | Режим 5: запускаемый аппаратно стробоскоп (перезапуск) | ||

| счетчик | формат | Режим | 0 | Счетчик - это 16-битный двоичный счетчик (0–65535). | ||||

| счетчик | формат | Режим | 1 | Счетчик четырехзначный двоично-десятичный код счетчик (0–9999) | ||||

| 1 | 1 | считать | статус | C2 | C1 | C0 | Икс | Команда обратного чтения (только 8254) |

| 1 | 1 | 0 | 0 | C2 | C1 | C0 | Икс | При следующем чтении выбранных счетчиков будет прочитан статус фиксации, затем будет подсчитано |

| 1 | 1 | 0 | 1 | C2 | C1 | C0 | Икс | При следующем чтении выбранных счетчиков будет считываться счетчик с защелкой. |

| 1 | 1 | 1 | 0 | C2 | C1 | C0 | Икс | При следующем чтении выбранных счетчиков будет прочитан статус фиксации. |

| 1 | 1 | 1 | 1 | C2 | C1 | C0 | Икс | Ничего не делать (ничего не фиксировать на одном или всех счетчиках) |

| 1 | 1 | считать | статус | 0 | 0 | 0 | Икс | Ничего не делать (количество защелок и / или статус без счетчиков) |

| 1 | 1 | считать | статус | 1 | C1 | C0 | Икс | Команда обратного чтения применяется к счетчику 2 |

| 1 | 1 | считать | статус | C2 | 1 | C0 | Икс | Команда обратного чтения применяется к счетчику 1 |

| 1 | 1 | считать | статус | C2 | C1 | 1 | Икс | Команда обратного чтения применяется к счетчику 0 |

При установке PIT микропроцессор сначала отправляет управляющее сообщение, а затем сообщение счета в PIT. Процесс подсчета начнется после того, как PIT получит эти сообщения, и, в некоторых случаях, если он обнаружит рост край от входного сигнала GATE. Формат байта состояния. Бит 7 позволяет программному обеспечению отслеживать текущее состояние вывода OUT. Бит 6 указывает, когда счет может быть прочитан; когда этот бит равен 1, счетный элемент еще не загружен и не может быть считан процессором. Биты с 5 по 0 совпадают с последними битами, записанными в регистр управления.

| Бит № / Имя | Краткое описание | |||||||

|---|---|---|---|---|---|---|---|---|

| D7 Вывод Статус | D6 значение NULL считать | D5 RW1 | D4 RW0 | D3 M2 | D2 M1 | D1 M0 | D0 BCD | |

| 0 | Вывод равен 0 | |||||||

| 1 | Вывод 1 | |||||||

| 0 | Счетчик можно прочитать | |||||||

| 1 | Счетчик устанавливается | |||||||

| формат | Режим | BCD | Биты режима счетчика, определенные для регистра управляющего слова | |||||

Режимы работы

Биты D3, D2 и D1 управляющего слова устанавливают режим работы таймера. Всего есть 6 режимов; для режимов 2 и 3 бит D3 игнорируется, поэтому отсутствующие режимы 6 и 7 являются псевдонимами для режимов 2 и 3.

Все режимы чувствительны к входу GATE, при этом высокий уровень GATE вызывает нормальную работу, но эффекты низкого уровня GATE зависят от режима:

- Режимы 0 и 4: подсчет приостанавливается, пока GATE низкий, и возобновляется, когда GATE высокий.

- Режимы 1 и 5: нарастающий фронт GATE начинает отсчет. GATE может перейти на низкий уровень, не влияя на счет, но другой нарастающий фронт перезапустит счет с начала.

- Режимы 2 и 3: GATE low немедленно принудительно устанавливает высокий уровень OUT (не дожидаясь тактового импульса) и сбрасывает счетчик (на следующем заднем фронте тактового сигнала). Когда GATE снова переходит на высокий уровень, счет начинается с начала.

Режим 0 (000): прерывание по счетчику клемм

Режим 0 используется для генерации точной временной задержки под управлением программного обеспечения. В этом режиме счетчик начнет отсчет от загруженного в него начального значения COUNT до 0. Скорость счета равна входной тактовой частоте.

На выводе OUT устанавливается низкий уровень после записи контрольного слова, и отсчет начинается через один такт после программирования COUNT. OUT остается на низком уровне, пока счетчик не достигнет 0, после чего OUT будет установлен на высоком уровне до тех пор, пока счетчик не будет перезагружен или не будет записано управляющее слово. Прилавок оборачивается, чтобы 0xFFFF внутренне и продолжает считать, но вывод OUT больше не меняется. Для нормального счета сигнал Gate должен оставаться активным на высоком уровне. Если Gate становится низким, счет приостанавливается и возобновляется, когда он снова становится высоким.

Первый байт нового счетчика при загрузке в регистр счетчика останавливает предыдущий счет.

Режим 1 (001): программируемый одиночный выстрел

В этом режиме 8253 может использоваться как Моностабильный мультивибратор. Вход GATE используется как вход триггера.

OUT изначально будет высоким. OUT перейдет на низкий уровень тактового импульса после запуска одноразового импульса и останется на низком уровне до тех пор, пока счетчик не достигнет нуля. Затем OUT станет высоким и останется высоким до импульса CLK после следующего запуска.

После записи контрольного слова и начального счета счетчик включается. Триггер приводит к загрузке счетчика и установке низкого уровня OUT для следующего импульса CLK, таким образом, запускается одноразовый импульс. Начальный счет N приведет к одноразовому импульсу длительностью N CLK циклов.

Одноразовый запуск можно перезапустить, поэтому OUT будет оставаться на низком уровне для N импульсов CLK после любого запуска. Одноразовый импульс можно повторить, не перезаписывая тот же счетчик в счетчике. GATE не влияет на OUT. Если новый счетчик записывается в счетчик во время однократного импульса, текущий однократный импульс не изменяется, если счетчик не запускается повторно. В этом случае в счетчик загружается новый счетчик, и импульс единичного импульса продолжается, пока не истечет новый счет.

Режим 2 (X10): генератор скорости

В этом режиме устройство действует как счетчик деления на n, который обычно используется для генерации прерывания часов реального времени.

Как и в других режимах, процесс подсчета запускает следующий тактовый цикл после отправки COUNT. OUT будет оставаться на высоком уровне до тех пор, пока счетчик не достигнет 1, и станет низким на один тактовый импульс. В следующем цикле счетчик перезагружается, OUT снова становится высоким, и весь процесс повторяется.

Время между высокими импульсами зависит от предварительно установленного значения в регистре счетчика и рассчитывается по следующей формуле:

Значение для загрузки в счетчик =

Обратите внимание, что значения в регистре COUNT варьируются от до 1; регистр никогда не достигает нуля.

Режим 3 (X11): генератор прямоугольных сигналов

Этот режим аналогичен режиму 2. Однако длительность высоких и низких тактовых импульсов на выходе будет отличаться от режима 2.

Предположим - число, загруженное в счетчик (сообщение COUNT), выход будет высоким для рассчитывает, и низкий для подсчитывает. Таким образом, период будет считается, а если является нечетным, дополнительный полупериод проводится с высоким уровнем OUT.

Режим 4 (100): программный строб

После загрузки управляющего слова и COUNT выход будет оставаться высоким, пока счетчик не достигнет нуля. Затем счетчик будет генерировать низкий импульс для 1 тактового цикла (строб) - после этого выход снова станет высоким.

GATE low приостанавливает счет, который возобновляется, когда GATE снова становится высоким.

Режим 5 (101): Строб с аппаратным запуском

Этот режим аналогичен режиму 4. Однако процесс счета запускается входом GATE.

После получения контрольного слова и COUNT на выходе будет установлен высокий уровень. Как только устройство обнаружит нарастающий фронт на входе GATE, оно начнет отсчет. Когда счетчик достигнет 0, на выходе будет низкий уровень на один такт - после этого он снова станет высоким, чтобы повторить цикл на следующем нарастающем фронте GATE.

Советы и подсказки по программированию IBM PC

8253 использовался в IBM PC-совместимых устройствах с момента их появления в 1981 году.[7] В наше время этот PIT не входит в состав ПК x86 как отдельный чип. Скорее, его функциональность включена в набор микросхем материнской платы. южный мост. В современном наборе микросхем это изменение может проявляться в виде заметно более быстрого доступа к регистрам PIT в x86 Адрес ввода / вывода Космос.

Все совместимые с ПК работают с PIT с тактовой частотой 105/88 = 1,193.18 МГц,1⁄3 то NTSC цветная вспышка частота. Эта частота, разделенная на 216 (самый большой делитель, на который способен 8253) производит прерывание по таймеру ≈18,2 Гц, используемое в MS-DOS и сопутствующие операционные системы.

В оригинальных ПК IBM счетчик 0 используется для генерации хронометраж прерывание. Счетчик 1 (A1 = 0, A0 = 1) используется для запуска обновления DRAM объем памяти. Последний счетчик (A1 = 1, A0 = 0) используется для генерации тонов через Динамик ПК.

Более новые материнские платы включают дополнительные счетчики через Расширенная конфигурация и интерфейс питания (ACPI), счетчик на расширенном локальном программируемом контроллере прерываний (Местный APIC), а Таймер событий высокой точности. Сам процессор также обеспечивает Счетчик отметок времени (TSC) объект.

На ПК адрес timer0 (чип) находится на порте 40h..43h, а второй timer1 (чип) находится на 50h..53h.

На компьютерах x86 BIOS многих видеокарт и системный BIOS перепрограммируют второй счетчик для собственного использования. Перепрограммирование обычно происходит во время изменений видеорежима, когда может быть запущена видео BIOS, и во время изменения режима управления системой и состояния энергосбережения, когда может быть запущена системная BIOS. Это предотвращает любые серьезные альтернативные варианты использования второго счетчика таймера во многих системах x86.

Таймер, который используется системой на компьютерах x86, - это канал 0, и его часы отсчитывают теоретическое значение 1193181,8181 ... Гц, т.е. одна треть NTSC цвет поднесущая частота, которая получается от деления системных часов (14,31818 МГц) на 12. Это пережиток самого первого CGA ПК - все необходимые частоты вывели из единого Кристалл кварца, и чтобы сделать телевизионный вывод возможным, этот генератор должен был работать на частоте, кратной частоте цветовой поднесущей NTSC.

Как указано выше, канал 0 реализован как счетчик. Как правило, начальное значение счетчика устанавливается путем отправки байтов в Control, затем регистры порта ввода-вывода данных (значение 36h отправляется на порт 43h, затем младший байт на порт 40h и снова порт 40h для старшего байта) . Счетчик считает вниз до нуля, затем отправляет аппаратное прерывание (IRQ 0, INT 8) в ЦПУ. Затем счетчик сбрасывается до исходного значения и снова начинает обратный отсчет. Максимально возможная частота прерывания составляет чуть более половины мегагерца. Самая низкая возможная частота, которая также обычно используется компьютерами, MS-DOS или совместимых операционных систем, составляет около 18,2 Гц. Под этими реальный режим В операционных системах BIOS накапливает количество вызовов INT 8, которые он получает по адресу 0040: 006c реального режима, который может быть прочитан программой.

Когда таймер отсчитывает обратный отсчет, его значение также можно прочитать напрямую, прочитав его порт ввода-вывода. дваждысначала для младшего байта, а затем для старшего байта. Однако в свободно работающих приложениях счетчика, таких как ПК x86, необходимо сначала написать защелка команду для желаемого канала в регистр управления, чтобы оба считанных байта принадлежали одному и тому же значению.

Согласно документу Microsoft 2002 года, «поскольку для чтения и записи на это оборудование [8254] требуется связь через порт ввода-вывода, программирование занимает несколько циклов, что непомерно дорого для ОС. Из-за этого апериодическая функциональность не используется на практике."[8]

Смотрите также

использованная литература

- ^ а б c "Интервальный таймер Intel 82C54 CHMOS Programme" (PDF) (техническая спецификация). Архивировано из оригинал (PDF) 7 мая 2016 г.

- ^ Д.А. Годзе; А.П. Годзе (2007). Продвинутые микропроцессоры. Технические публикации. п. 74. ISBN 978-81-89411-33-6.

- ^ http://pdf.datasheetcatalog.com/datasheet/Intel/mXvqwzr.pdf

- ^ Intel Corporation, "Focus Components: Military Intelligence: Timers, EPROMs, Leadless Chip Carriers", Solutions, март / апрель 1983 г., стр. 12.

- ^ «8254 / 82C54: Введение в программируемый интервальный таймер». Корпорация Intel. Архивировано из оригинал 22 ноября 2016 г.. Получено 21 августа 2011.

- ^ "Техническое описание MSM 82c53" (PDF).

- ^ «Рекомендации по поддержке мультимедийного таймера». 20 сентября 2002 г.. Получено 13 октября 2010.

- ^ Рекомендации по поддержке мультимедийного таймера

дальнейшее чтение

- Гиллуве, Фрэнк Ван (1997). Недокументированный ПК: Руководство программиста по вводу-выводу, процессорам и областям фиксированной памяти (вторая, иллюстрированная ред.). Эддисон-Уэсли. ISBN 978-0-201-47950-8.